TOSHIBA BiCD Integrated Circuit Silicon Monolithic

# TB6596FLG

# DC and Stepping Motor Driver IC

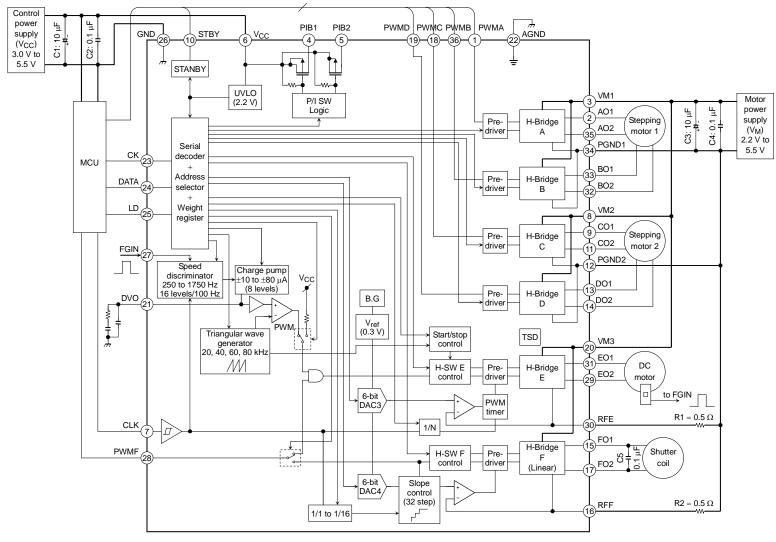

The TB6596FLG is a DC motor driver IC using LDMOS output transistors with low ON-resistance.

The TB6596FLG incorporates one PWM-constant-current H-bridge driver, four direct-PWM-controlled H-bridge drivers, and also one linear constant-current H-bridge driver. The TB6596FLG is best suited to control various lens actuators in digital still cameras

The three-wire serial interface provides control over the drivers, thus reducing the number of lines required for interfacing with the control IC.

Weight: 0.08 g (typ.)

#### **Features**

- Motor power supply voltage:  $V_M \le 6 \text{ V (max)}$

- Control power supply voltage: VCC = 3 to 6 V

- Output current: IouT ≤ 0.8 A (max)

- Complementary P- and N-channel LDMOS output transistors

- Output ON-resistance: Ron (upper and lower sum) =  $1.5 \Omega$  (typ.)

#### Channel E: DC Motor Driver

- High-speed PWM control at several hundred kHz

- Motor control method can be selected from the following two with the serial data inputs:

- 1. Controls motor speed by using both a frequency-locked-loop (FLL) speed discriminator that compares the FG and CLK signals, and an integrator.

- (Typical speed = Between 250 Hz and 1750 Hz in 16 steps.)

- 2. Controls H-bridge by using a direct PWM input.

- Two power switching transistors for optical encoder

#### Channel A and B or Channel C and D: Stepping Motor Driver

• Four H-bridge drivers (channel A and B, channel C and D) for direct PWM control. (Capable of controlling up to two 2-phase bipolar stepping motors or four DC motors.)

#### Channel F: Shutter Driver

- Linear constant-current drivers

- Current ramp-up rate control for improving the dependency of a current ramp-up slope on supply voltage change at startup and also for improving its reproducibility.

- (Increases current in up to 32 steps by using the internal CLK, which is derived by dividing CLK by 1 to 16.)

#### Other Features

- Two 6-bit DACs provide reference values for each constant-current limiters

- Dedicated standby (power-save) pin

- Thermal shutdown (TSD): Disables the output bias generator when the internal junction temperature exceeds 170°C.

- Undervoltage lockout (UVLO): Resets and disables the internal circuitry when VCC falls below 2.2 V (typ.)

- Small QON-36 package (0.5-mm lead pitch)

- Compatible with Pb-free reflow soldering

Note: This product has a MOS structure and is sensitive to electrostatic discharge. When handling this product, ensure that the environment is protected against electrostatic discharge by using an earth strap, a conductive mat and an ionizer. Ensure also that the ambient temperature and relative humidity are maintained at reasonable levels.

About solderability, following conditions were confirmed

- Solderability

- (1) Use of Sn-37Pb solder Bath

- $\cdot \ \ \text{solder bath temperature} = 230^{\circ}\text{C}$

- dipping time = 5 seconds

- · the number of times = once

- · use of R-type flux

- (2) Use of Sn-3.0Ag-0.5Cu solder Bath

- · solder bath temperature = 245°C

- · dipping time = 5 seconds

- the number of times = once

- · use of R-type flux

## **Block Diagram**

# **Absolute Maximum Ratings (Ta = 25°C)**

| Charac                | Characteristics |                  | Rating     | Unit | Remarks            |

|-----------------------|-----------------|------------------|------------|------|--------------------|

| Supply voltage        |                 | Vcc              | 6          | V    | Vcc                |

| Motor supply voltage  |                 | V <sub>M</sub>   | 6          | V    | $V_{M}$            |

| Output voltage        |                 | V <sub>OUT</sub> | 6          | V    |                    |

| Output ourrent        | H-SW            | Гоит             | 0.8        | Α    |                    |

| Output current        | PI SW Tr.       | I <sub>D</sub>   | 0.1        | A    | PIB1, PIB2         |

| Input voltage         |                 | V <sub>IN</sub>  | -0.2 to 6  | V    | Control input pins |

| Power dissination     |                 | D-               | 0.6        | W    | IC only            |

| Power dissipation     |                 | P <sub>D</sub>   | 1.04       | VV   | (Note)             |

| Operating temperature |                 | T <sub>opr</sub> | -20 to 85  | °C   |                    |

| Storage temperatu     | ire             | T <sub>stg</sub> | -55 to 150 | °C   |                    |

Note: When mounted on a glass epoxy single-sided PCB (size:  $50 \text{ mm} \times 50 \text{ mm} \times 1.6 \text{ mm}$ ) with a 40% dissipating copper surface.

# Operating Ranges ( $Ta = -20 \text{ to } 85^{\circ}\text{C}$ )

| Chara                                     | otoriotico        | Symbol           | Rating |      |     | Unit | Remarks                             |

|-------------------------------------------|-------------------|------------------|--------|------|-----|------|-------------------------------------|

| Characteristics                           |                   | Symbol           | Min    | Тур. | Max | Oill | Remarks                             |

| Supply voltage for small-signal circuitry |                   | V <sub>CC</sub>  | 3      | 3.3  | 5.5 | V    |                                     |

| Motor supply voltage                      |                   | V <sub>M</sub>   | 2.2    | 3.3  | 5.5 | V    |                                     |

|                                           | H-SW              | l <sub>ОИТ</sub> | _      | _    | 600 |      | $V_M = 3 \text{ to } 5.5 \text{ V}$ |

| Output current                            |                   |                  | _      | _    | 350 | mA   | $2.2~V \leq V_M < 3~V$              |

|                                           | PI SW Transistors | I <sub>D</sub>   | _      | _    | 30  |      |                                     |

| PWM frequency (Channels A to E)           |                   | f <sub>PWM</sub> | _      | _    | 100 | kHz  |                                     |

| CLK driver frequer                        | ncy               | f <sub>CLK</sub> | _      | 1    | 5   | MHz  |                                     |

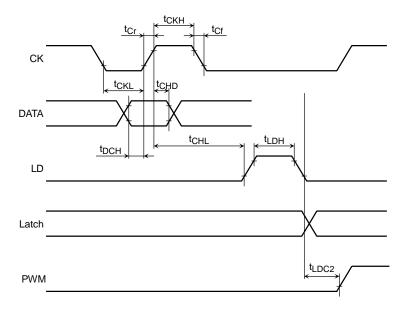

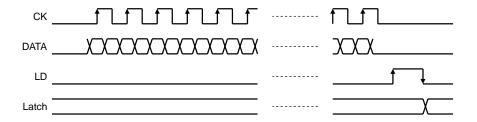

# Operating Ranges: Serial Data Controller (Ta = -20 to 85°C)

| Characteristics            | Symbol            | Ra  | ting | Unit  |

|----------------------------|-------------------|-----|------|-------|

| Characteristics            | Symbol            | Min | Max  | Offic |

| Clock pulse width Low      | tCKL              | 200 | _    | ns    |

| Clock pulse width High     | t <sub>CKH</sub>  | 200 | _    | ns    |

| Clock rise time            | t <sub>Cr</sub>   |     | 50   | ns    |

| Clock fall time            | tCf               | 1   | 50   | ns    |

| Data setup time            | t <sub>DCH</sub>  | 30  | _    | ns    |

| Data hold time             | tCHD              | 60  | _    | ns    |

| CK to LD rising edge       | tCHL              | 200 | _    | ns    |

| LD to PWM delay            | t <sub>LDC2</sub> | 100 | _    | ns    |

| Load pulse width High      | tLDH              | 2   |      | μS    |

| CK (clock pulse) frequency | fcLK              | _   | 2.5  | MHz   |

# **Principle of Operation**

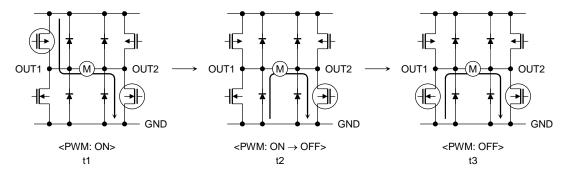

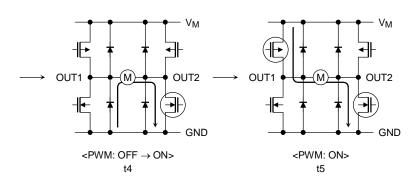

# Bridge Outputs: Basic operation of channels A through E PWM Control

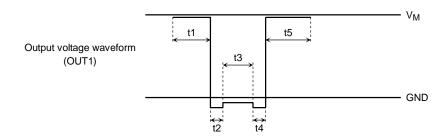

In PWM constant-current mode, the PWM chopper circuit alternates between on (t1, t5) and short brake (t3).

(To eliminate shoot-through current, a dead time (t2, t4) is inserted when the PWM is turned on and off.)

# Constant-Current Bridge Driver (Channel E): PWM constant-current choppers

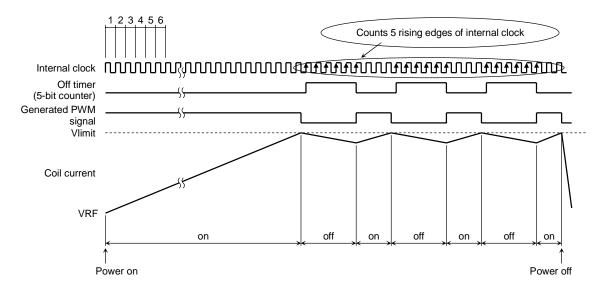

The TB6596FLG has PWM choppers with a constant turn-off period.

The turn-off period is measured by counting the number of rising edges of an internal clock signal, which is generated by dividing the external CLK signal. The turn-off period can be adjusted by changing either the CLK frequency or the number of its rising edges counted (three or five counts; the default is five counts).

Turning on the power supply causes a current to flow into the motor coils. The peak current through the winding is sensed via an external current-sensing resistor. As the current increases, a voltage (VRF) develops across the resistor, which is fed back to the internal comparator. At the predetermined reference voltage (Vlimit: current limiting voltage), the comparator turns off (chops) the power supply.

When high-side output transistors are turned off, the TB6596FLG, by default, counts five rising edges of the internal clock signal as a turn-off period. (The counter resets at the sixth rising edge of the clock.)

Based on this turn-off period, the TB6596FLG generates a PWM signal that turns on and off the output transistors.

#### Timing Diagram of the PWM Constant-Current Chopper Circuit with the Default Turn-Off Period

7

(The upper limit of the coil current (IO peak) can be calculated as: IO = Vlimit/RNF.)

# **Linear Constant-Current Bridge: Channel F**

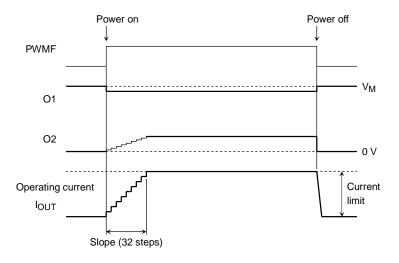

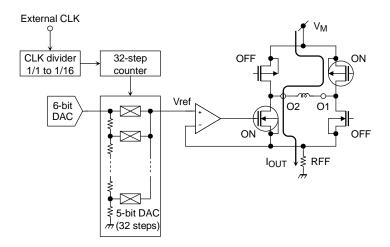

This bridge driver circuit is tuned on and off by setting the PEMF pin High and Low, respectively.

The driver output current is converted to a voltage through the external resistor RFF and fed back to a sense amplifier, thus creating a negative feedback loop. This enables the constant-current drive using the low-side driver.

The constant-current value is adjusted by changing the Vref input to the sense amplifier, which is specified by an internal 6-bit DAC ( $\max = 0.3 \text{ V}$ ).

# \*Current ramp-up rate controller:

To improve the dependency of a current ramp-up slope on supply voltage change at startup and its reproducibility according to the time constant of the coil, the reference voltage for the comparator is increased using a 5-bit DAC (in 32 steps) up to the current limit. This can stabilize the reproducibility of a current ramp-up slope.

The current ramp-up rate is specified by dividing an external CLK. The frequency divider ratio can be selected from 16 options (1/1 to 1/16) by using 4-bit serial data inputs.

# **Speed Control**

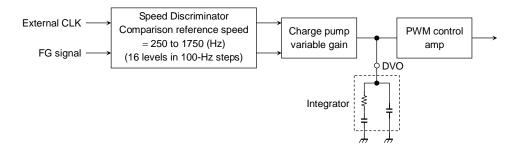

- The FLL speed discriminator compares the FG signal against the reference speed which is derived from an

external CLK.

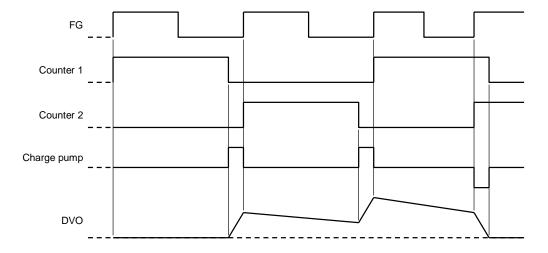

- The speed discriminator has two counters that alternately count one cycle of the FG signal. It then generates

error pulses (charge and discharge) according to the frequency difference. Based on these pulses, the integrator

(set by an external RC) and the PWM control amplifier generates a motor drive output signal to control the motor

rotational speed.

- The reference speed of the speed discriminator is selectable from 16 levels between 250 and 1750 Hz in 100-Hz steps. (It is selected by serial data inputs.)

- The motor rotation speed (N) is calculated by the following equation:

$N (rpm) = f_{CLK} (Hz)/CT \times 60/Z$

Z: Number of FG pulses per rotor rotation

CT: Speed discriminator count

# **Charge Pump Circuit**

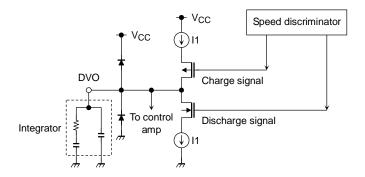

- Consisting of CMOS transistors, this charge pump achieves a high resolution of the speed control signal.

- The gain of the speed discriminator can be internally selected from eight combinations of charging and discharging current values (±10 to 80 µA). And the total control gain is determined by adjusting the charge pump current and the time constant of the external integrator.

- When the motor is not rotating, this circuit remains in discharge mode ( $-50 \mu A$ ). Thus, the amount of charge stored in a capacitor of the external integrator becomes zero resetting the analog control value.

- Since the FG signal is not generated immediately after the PWME drive signal assertion due to the stationary motor, the speed control loop is not enabled at this time. Therefore, the forced commutation signal (Duty cycle = 100%) is applied as a motor driving signal for a short period of time from the rising edge of the PWME signal.

- \* The motor startup time can be selected from 64 options (0 to 63) in 2.048-ms steps by a 6-bit serial command.

- For powering off, the motor operation of a certain period of time after the falling edge of the PWM signal can be selected from the brake and the reverse-plus-brake modes.

- \* The reverse rotation time can be selected from 64 options (0 to 63) in 2.048-ms steps by a 6-bit serial command.

# **Input Pins:**

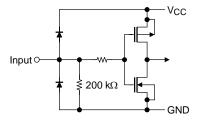

All input pins (CK, DATA, LD, PWME, PWMF, STBY, CLK) have a pull-down resistor of about 200 k $\Omega$ . The FGIN pin is pulled up to  $V_{CC}$  via a pull-up resistor of about 200 k $\Omega$ .

#### CK, DATA, LD, PWMA, B, C, D, PWMF, STBY, CLK

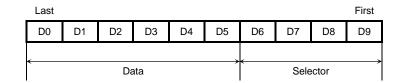

# Serial Data Format 10-Bit Serial Data

#### **Each Resister Mode**

| D9 | D8 | D7 | D6 | D5        | D4                                            | D3         | D2            | D1         | D0         | Address |

|----|----|----|----|-----------|-----------------------------------------------|------------|---------------|------------|------------|---------|

| 0  | 0  | 0  | 0  | p2a       | p2b                                           | p1a        | p1b           | _          | _          | 0       |

| 0  | 0  | 0  | 1  | mod2      | mod1                                          | pm2        | pm1           | _          | _          | 1       |

| 0  | 0  | 1  | 0  | p4a       | p4b                                           | рЗа        | p3b           | _          | -          | 2       |

| 0  | 0  | 1  | 1  | mod4      | mod3                                          | pm4        | pm3           | _          |            | 3       |

| 0  | 1  | 0  | 0  | Reverse   | Reverse brake time(0 to 127 ms)               |            |               |            |            | 4       |

| 0  | 1  | 0  | 1  | р5а       | p5b                                           | VC         | pms           | sw2        | sw1        | 5       |

| 0  | 1  | 1  | 0  | mod5      | mod5 pm5 lf5 Charge pump gain (3 bits)        |            |               |            |            | 6       |

| 0  | 1  | 1  | 1  | Target sp | Target speed value (4 bits) Carrier frequency |            |               |            |            | 7       |

| 1  | 0  | 0  | 0  | Forced o  | ommutati                                      | on time fo | r startup (   | 0 to 127 r | ns)        | 8       |

| 1  | 0  | 0  | 1  | DA5 (6 b  | its): Sets                                    | the currer | nt level for  | channel    | E          | 9       |

| 1  | 0  | 1  | 0  | р6а       | p6b                                           | Constan    | nt-current ra | amp-up rat | e (4 bits) | 10      |

| 1  | 0  | 1  | 1  | mod6      | pm6                                           | lf6        | _             | _          | -          | 11      |

| 1  | 1  | 0  | 0  | DA6 (6 b  | its): Sets                                    | the currer | nt level for  | channel    | F          | 12      |

| 1  | 1  | 0  | 1  | _         |                                               |            |               |            |            | 13      |

| 1  | 1  | 1  | 0  | _         |                                               | _          |               |            | _          | 14      |

| 1  | 1  | 1  | 1  |           | _                                             | _          | off           | _          | _          | 15      |

Ifx: Current control for channels E and F (0 = Enable; 1 = Disable)

Pms: Channel switching of the PMW input (0 = channel E; 1 = channel F)

Off: Chop-off count (0 = 5 internal clock cycles, 1 = 3 internal clock cycles)

Swx: Turns on/off SW1 and SW2 (0 = off; 1 = on)

Vc: Channel E control mode (0 = External PWM control; 1 = Internal FLL speed control)

Reverse brake: Sets the reverse brake time to be  $2.048~\text{ms} \times \text{specified}$  value

Forced commutation time for startup: Full drive for a period of 2.048 ms × specified value after startup

Charge pump gain: These 3 bits specify the gain of the charge pump to one of the 8 levels between  $\pm 10~\mu A$  to  $\pm 80~\mu A$  in 10- $\mu A$  steps.

Career frequency: These 2 bits specify the triangular wave frequency to one of the frequencies:  $20~\mathrm{kHz}$ ,  $40~\mathrm{kHz}$ ,  $60~\mathrm{kHz}$  and  $80~\mathrm{kHz}$ .

11

Speed target: These 4 bits specify the speed target value to any of the 16 speed between 250 Hz to 1750 Hz in 100-Hz steps.

Constant current ramp-up rate: Controls the current ramp-up slope for channel F by changing the number of

internal clock cycle count. (0 to 15 cycles: Steps up the DAC output voltage at every specified count.)

#### (\*) Address 15 setting

- (1) All register data are cleared (set to "0") if user set all "0" at address 15. Avoid the setting all "0" at the address or set at other address after setting at address 15.

- (Chop-off count should be 5 clock cycles in default state means even without setting at this.)

- (2) D1 and D0 in address 15 are forbidden area. Avoid setting "1" at D1 and D0.

# **Driver Operating Modes**

modx = 0, pmx = 0

| pxa | pxb | PMx | OUTxA | OUTxB | Driving Mode |

|-----|-----|-----|-------|-------|--------------|

| 0   | 0   | Х   | Z     | Z     | Stop         |

| 0   | 1   | L   | L     | L     | Short brake  |

| 0   | 1   | Н   | L     | Н     | Reverse      |

| 1   | 0   | L   | L     | L     | Short brake  |

| 1   | 0   | Н   | Н     | L     | Forward      |

| 1   | 1   | Х   | L     | L     | Short brake  |

# modx = 0, pmx = 1

| pxa | pxb | PMx | OUTxA | OUTxB | Driving Mode |

|-----|-----|-----|-------|-------|--------------|

| 0   | 0   | Х   | Z     | Z     | Stop         |

| 0   | 1   | L   | L     | Н     | Reverse      |

| 0   | 1   | Н   | L     | L     | Short brake  |

| 1   | 0   | L   | Н     | L     | Forward      |

| 1   | 0   | Н   | L     | L     | Short brake  |

| 1   | 1   | X   | L     | L     | Short brake  |

modx = 1, pmx = X

| pxa | pxb | PMx | OUTxA | OUTxB | Driving Mode |

|-----|-----|-----|-------|-------|--------------|

| 0   | X   | Х   | Z     | Z     | STOP         |

| 1   | 0   | L   | Н     | L     | Forward      |

| 1   | 0   | Н   | L     | Н     | Reverse      |

| 1   | 1   | X   | L     | L     | Short brake  |

Note: Only valid for channel E. (Reverse brake function)

When short brake mode is selected, the motor operation is controlled in the following sequence.

Reverse brake → Short brake

- The reverse brake time is specified by serial data. (When Reverse brake time = 0, the TB6596FLG does not enter Reverse brake mode.)

- During the reverse brake operation, the operating mode cannot be changed.

- When the PMx input changes during the short brake operation at modx = 0, the

operating mode changes according to the spxa and pxb inputs as shown in the above

table. (Direct PWM control)

# Electrical Characteristics (unless otherwise specified, $V_{CC}=3.3~V,\,V_{M}=5~V,\,Ta=25^{\circ}C)$

| Ch                                                       | aracteristics             |                          | Symbol                    | Test Condition                                              | Min                      | Тур.  | Max                      | Unit |  |

|----------------------------------------------------------|---------------------------|--------------------------|---------------------------|-------------------------------------------------------------|--------------------------|-------|--------------------------|------|--|

|                                                          |                           |                          | Icc                       | All 6 channels in Forward mode                              | _                        | 1     | 2.5                      | mA   |  |

| Supply current                                           |                           |                          | I <sub>CC</sub> (STB)     | Standby mode (STBY = 0 V)                                   | _                        | 0.1   | 10                       |      |  |

|                                                          |                           |                          | I <sub>M (STB)</sub>      | - Standby mode (STBY = 0 V)                                 | _                        | 0     | 1                        | μА   |  |

| 0 1 1 0 7 7 1                                            | Input voltage             | Input voltage            |                           |                                                             | V <sub>CC</sub><br>- 0.8 | _     | V <sub>CC</sub><br>+ 0.2 | V    |  |

| Serial, STBY,<br>PWM and CLK<br>nputs                    |                           |                          | $V_{INL}$                 |                                                             | -0.2                     | _     | 0.4                      |      |  |

| inputs                                                   | Input current             |                          | I <sub>INH</sub>          | V <sub>IH</sub> = 3 V                                       | 10                       | 15    | 20                       | μΑ   |  |

|                                                          | input current             |                          | I <sub>INL</sub>          | $V_{IL} = 0 V$                                              | _                        | _     | 1                        | μΛ   |  |

|                                                          | Input voltage             |                          | V <sub>INHFG</sub>        |                                                             | V <sub>CC</sub><br>- 0.8 | _     | V <sub>CC</sub><br>+ 0.2 | V    |  |

| FG input                                                 |                           |                          | VINLFG                    |                                                             | -0.2                     | —     | 0.4                      |      |  |

|                                                          | Input current             |                          | I <sub>INSH</sub>         | V <sub>IH</sub> = 3 V                                       | _                        | —     | 1                        | μА   |  |

|                                                          | Input current             |                          | I <sub>INSL</sub>         | $V_{IL} = 0 V$                                              | -20                      | -15   | -10                      | μΛ   |  |

| Output saturation voltage                                |                           | V <sub>sat (U + L)</sub> | $I_{O} = 0.2 \text{ A}$   | _                                                           | 0.3                      | 0.4   | V                        |      |  |

| (Channels A to F                                         | (Channels A to F)         |                          | vsat (U + L)              | $I_{O} = 0.6 A$                                             | _                        | 0.9   | 1.2                      | v    |  |

| Output leakage current                                   |                           |                          | I <sub>L (U)</sub>        | V <sub>M</sub> = 6 V                                        | _                        | _     | 1                        | μА   |  |

| Channels A to F)                                         |                           | I <sub>L (L)</sub>       | VIVI — O V                | _                                                           | _                        | 1     | μ                        |      |  |

| Output diada for                                         | diode forward voltage     |                          | V <sub>F (U)</sub>        | I <sub>F</sub> = 0.6 A (Design value)                       | _                        | 1     | _                        | V    |  |

| utput diode forward voltage                              |                           | V <sub>F (L)</sub>       | TF = 0.0 A (Design value) | _                                                           | 1                        | _     | V                        |      |  |

| Offset voltage for constant-current detection comparator |                           |                          | Comp ofs                  | RRF = 1 $\Omega$ , V <sub>ref</sub> = 0.1 V (including DAC) | -10                      | _     | 10                       | m\   |  |

|                                                          | Charge current            | Min                      | ICHG Min                  | VDO = 1 V (Design target only)                              | _                        | 10    |                          | μΑ   |  |

|                                                          |                           | Max                      | ICHG Max                  |                                                             | _                        | 80    | _                        |      |  |

| Charge pump                                              |                           | Step                     | ICHG step                 |                                                             | _                        | 10    | _                        |      |  |

| Charge pump                                              | Discharge<br>current      | Min                      | IDIS Min                  |                                                             | _                        | -10   | _                        |      |  |

|                                                          |                           | Max                      | IDIS Max                  | VDO = 2 V (Design target only)                              | _                        | -80   | _                        |      |  |

|                                                          |                           | Step                     | IDIS step                 |                                                             | _                        | -10   | _                        |      |  |

| 6-bit DAC                                                | Nonlinearity              |                          | LB                        | - Channels E and F                                          | -3                       | _     | 3                        | LSB  |  |

| 0-DIL DAG                                                | Differential linear       | ity error                | DLB                       | - Chamileis E and F                                         | -2                       | _     | 2                        |      |  |

| P/I SW<br>Transistors                                    | Output saturation voltage | 1                        | Vsat                      | ID = 20 mA                                                  | _                        | _     | 0.1                      | V    |  |

| 114115151015                                             | Output leakage o          | urrent                   | IDSS                      | VDS = 6 V                                                   | _                        | _     | 1                        | μΑ   |  |

|                                                          | Minimum speed             | Minimum speed            |                           |                                                             | _                        | 250   | _                        |      |  |

| Speed control                                            | Maximum speed             |                          | FLL Max                   | (Design target only)                                        | _                        | 1750  | _                        | Hz   |  |

|                                                          | Speed step                |                          | FLL step                  |                                                             | _ 100 _                  |       | _                        |      |  |

|                                                          | Minimum speed             |                          | Ftrig Min                 |                                                             | _                        | 17    | _                        |      |  |

| Triangular wave carrier                                  | Maximum speed             | Maximum speed            |                           | (Design target only)                                        | _                        | 68    | _                        | kH   |  |

| -                                                        | Speed step                |                          | Ftrig step                |                                                             | _                        | 17    | _                        |      |  |

|                                                          | Minimum control           | time                     | Tmin                      |                                                             | _                        | 0     | _                        | ms   |  |

| Start/Reverse                                            | Maximum control           | l time                   | Tmax                      | (Design target only)                                        | _                        | 129   | _                        |      |  |

|                                                          | Control time step         | )                        | T step                    | 1                                                           | _                        | 2.048 | _                        |      |  |

| Thermal shutdov                                          | vn threshold              |                          | TSD                       | (Desire toward out )                                        | _                        | 170   | _                        |      |  |

| Thermal shutdov                                          | vn hysteresis             |                          | ΔTSD                      | (Design target only)                                        | _                        | 20    | _                        | °C   |  |

## **Application Circuit**

- Bypass capacitors (C1, C2, C3, C4) should be connected as close to the IC as possible.

- The Cdp capacitor of 0.01 to  $0.1~\mu F$  should be connected to channel-F outputs as necessary to prevent the oscillation.

Notes: Excessive power might be introduced into the IC in case of a short-circuit between power supply and ground, an output short-circuit to power supply, an output short-circuit to ground or a short-circuit across the load. If any of these events occur, the device may be degraded or permanently damaged.

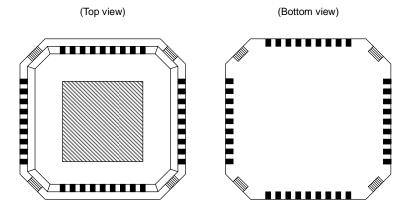

# QON Package Considerations Package Appearances

Please follow the following guidelines for the QON package.

#### **Guidelines:**

- (1) The solder plated pads at the four corners of the package (shaded areas in the bottom view) should not be soldered for the purpose of improving the mechanical strength of solder joints.

- (2) When using the TB6596FLG, it should be ensured that the thermal pad and solder plated pads (shaded areas in the top and bottom views) are electrically insulated (Note).

Note: Care should be taken in the board design to prevent solder for through-hole joints from flowing to the solder plated pads on the bottom of the package (shaded areas in the bottom view).

- When mounting or soldering this package, care must be taken to avoid electrostatic discharge or

electrical overstress to the IC. (This is to avoid electrical leakage and a buildup of electrostatic

charge in the end product.)

- It should be ensured that no voltage is directly applied to the solder plated pads when designing

the PC board.

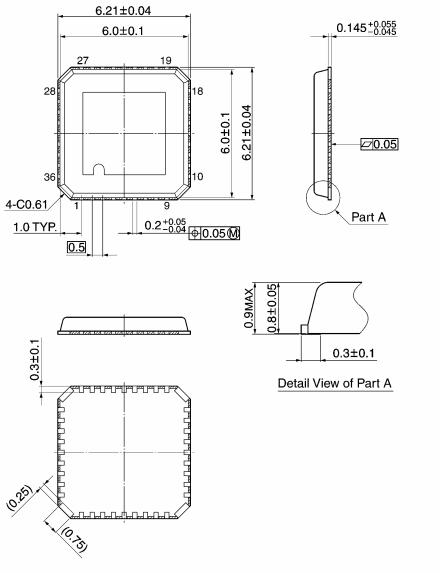

# **Package Dimensions**

QON36-P-0606-0.50 Unit: mm

Note 1: The solder-plated parts at the four corners of the package should not be used as external pins.

Note 2: The four corners of the package should not be soldered.

Note 3: Shaded areas: Resin surfaces

Weight: 0.08 g (typ.)

#### **Notes on Contents**

## 1. Block Diagrams

Some of the functional blocks, circuits, or constants in the block diagram may be omitted or simplified for explanatory purposes.

## 2. Equivalent Circuits

The equivalent circuit diagrams may be simplified or some parts of them may be omitted for explanatory purposes.

# 3. Timing Charts

Timing charts may be simplified for explanatory purposes.

#### 4. Application Circuits

The application circuits shown in this document are provided for reference purposes only. Thorough evaluation is required, especially at the mass production design stage.

To shiba does not grant any license to any industrial property rights by providing these examples of application circuits.

#### 5. Test Circuits

Components in the test circuits are used only to obtain and confirm the device characteristics. These components and circuits are not guaranteed to prevent malfunction or failure from occurring in the application equipment.

# IC Usage Considerations

# Notes on Handling of ICs

smoke or ignition.

- (1) The absolute maximum ratings of a semiconductor device are a set of ratings that must not be exceeded, even for a moment. Do not exceed any of these ratings.

Exceeding the rating(s) may cause the device breakdown, damage or deterioration, and may result injury by explosion or combustion.

- (2) Use an appropriate power supply fuse to ensure that a large current does not continuously flow in case of over current and/or IC failure. The IC will fully break down when used under conditions that exceed its absolute maximum ratings, when the wiring is routed improperly or when an abnormal pulse noise occurs from the wiring or load, causing a large current to continuously flow and the breakdown can lead smoke or ignition. To minimize the effects of the flow of a large current in case of breakdown, appropriate settings, such as fuse capacity, fusing time and insertion circuit location, are required.

- (3) If your design includes an inductive load such as a motor coil, incorporate a protection circuit into the design to prevent device malfunction or breakdown caused by the current resulting from the inrush current at power ON or the negative current resulting from the back electromotive force at power OFF. IC breakdown may cause injury, smoke or ignition.

Use a stable power supply with ICs with built-in protection functions. If the power supply is unstable, the protection function may not operate, causing IC breakdown. IC breakdown may cause injury,

- 4) Do not insert devices in the wrong orientation or incorrectly. Make sure that the positive and negative terminals of power supplies are connected properly. Otherwise, the current or power consumption may exceed the absolute maximum rating, and exceeding the rating(s) may cause the device breakdown, damage or deterioration, and may result injury by explosion or combustion. In addition, do not use any device that is applied the current with inserting in the wrong orientation or incorrectly even just one time.

# Points to Remember on Handling of ICs

#### (1) Thermal Shutdown Circuit

Thermal shutdown circuits do not necessarily protect ICs under all circumstances. If the thermal shutdown circuits operate against the over temperature, clear the heat generation status immediately. Depending on the method of use and usage conditions, such as exceeding absolute maximum ratings can cause the thermal shutdown circuit to not operate properly or IC breakdown before operation.

#### (2) Heat Radiation Design

In using an IC with large current flow such as power amp, regulator or driver, please design the device so that heat is appropriately radiated, not to exceed the specified junction temperature (Tj) at any time and condition. These ICs generate heat even during normal use. An inadequate IC heat radiation design can lead to decrease in IC life, deterioration of IC characteristics or IC breakdown. In addition, please design the device taking into considerate the effect of IC heat radiation with peripheral components.

#### (3) Back-EMF

When a motor rotates in the reverse direction, stops or slows down abruptly, a current flow back to the motor's power supply due to the effect of back-EMF. If the current sink capability of the power supply is small, the device's motor power supply and output pins might be exposed to conditions beyond maximum ratings. To avoid this problem, take the effect of back-EMF into consideration in system design.

#### **RESTRICTIONS ON PRODUCT USE**

070122EBA\_R6

- The information contained herein is subject to change without notice. 021023\_D

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor

devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical

stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety

in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such

TOSHIBA products could cause loss of human life, bodily injury or damage to property.

- In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc. 021023\_A

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk. 021023\_B

- The products described in this document shall not be used or embedded to any downstream products of which

manufacture, use and/or sale are prohibited under any applicable laws and regulations. 060106\_Q

- The information contained herein is presented only as a guide for the applications of our products. No responsibility

is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from

its use. No license is granted by implication or otherwise under any patents or other rights of TOSHIBA or the third

parties. 070122\_C

- Please use this product in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances.

- Toshiba assumes no liability for damage or losses occurring as a result of noncompliance with applicable laws and regulations. 060819\_AF

- The products described in this document are subject to foreign exchange and foreign trade control laws. 060925\_E

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Toshiba:

TB6596FLG(O,EL)